Pengertian SPARC (Scalable Processor Architecture)

SPARC (Scalable Processor Architecture) adalah microprocessor berarsitektur RISC (Reduced Instruction Set Computer) yang didesain oleh Sun Microsystems tahun 1985. SPARC ialah merek jualan terdaftar dari SPARC International, Inc, sebuah organisasi yang diresmikan pada tahun 1989 untuk mengiklankan arsitektur SPARC dan untuk melaksanakan pengujian. SPARC Internasional berencana untuk membuka arsitektur SPARC demi menciptakan ekosistem yang lebih besar bagi pengembangan desainnya, yang izinnya sudah diberikan kepada beberapa manufaktur, termasuk Texas Instruments, Atmel, Cypress Semiconduktor, dan Fujitsu. Sehingga arsitektur SPARC terbuka penuh dan non-langsung.

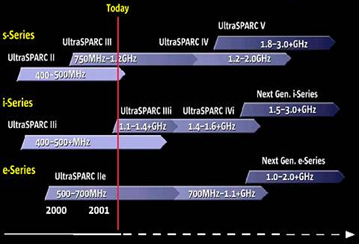

Gambar Alur Prosesor SPARC

Implementasi arsitektur SPARC pada awalnya dirancang dan digunakan untuk metode Sun-4 workstation dan server, mengambil alih versi sebelumnya Sun-3 yang berbasis keluarga proseso rMotorola 68000. Kemudian, prosesor SPARC digunakan di server SMP (Symmetric multiprocessing) yang antara lain dibuat oleh Sun Microsystems, Solbourne dan Fujitsu.SPARC (Scalable Processor dari Arsitektur) ialah RISC arsitektur set aba-aba (ISA) yang dikembangkan oleh Sun Microsystems dan diperkenalkan pada pertengahan 1987.

SPARC yaitu merek jualan terdaftar dari SPARC International, Inc , sebuah organisasi yang didirikan pada tahun 1989 untuk mempromosikan arsitektur SPARC, mengorganisir merek jualan SPARC, dan memperlihatkan pengujian kesesuaian . Implementasi yang asli 32-bit arsitektur SPARC pada awalnya dirancang dan dipakai di Sun 4 Sun- workstation dan server tata cara, menggantikan mereka sebelumnya Sun-3 metode berbasis pada Motorola 68000 keluarga prosesor. Kemudian, prosesor SPARC dipakai di SMP server yang diproduksi oleh Sun Microsystems , Solbourne dan Fujitsu , antara lain, dan dirancang untuk 64-bit operasi.

SPARC International dimaksudkan untuk membuka arsitektur SPARC untuk membuat ekosistem yang lebih besar untuk desain, yang sudah dilisensikan ke beberapa produsen, tergolong Texas Instruments , Atmel , Cypress Semiconductor , dan Fujitsu . Sebagai hasil dari SPARC International, arsitektur SPARC terbuka sarat dan non-eksklusif.

Pada bulan Maret 2006, desain lengkap UltraSPARC T1 mikroprosesor ‘Sun Microsystems dirilis source-dalam-bentuk terbuka di OpenSPARC.net dan bernama OpenSPARC T1. Pada tahun 2007, desain UltraSPARC T2 mikroprosesor’s Sun juga dirilis dalam bentuk open-source, selaku OpenSPARC T2, lihat OpenSPARC.net .

Pada Juni 2009, rancangan SPARC digunakan oleh Fujitsu Laboratories Ltd untuk menciptakan produk prosesor berjulukan Venus SPARC64 VIIIfx yang mampu 128 miliar operasi floating point per detik (128 GFlops). Arsitektur SPARC sungguh dipengaruhi oleh rancangan RISC sebelumnya tergolong RISC I dan II dari University of California, Berkeley dan IBM 801 . RISC ini yakni asli rancangan minimalis, termasuk selaku beberapa fitur atau op-aba-aba mungkin dan bermaksud untuk mengeksekusi isyarat pada tingkat nyaris satu arahan per siklus clock . Hal ini membuat mereka mirip dengan arsitektur MIPS dalam banyak hal, tergolong kurangnya instruksi mirip mengalikan atau membagi. Fitur lain dari SPARC dipengaruhi oleh gerakan RISC awal yakni delay slot cabang .

Prosesor SPARC biasanya berisi sebanyak 160 register tujuan biasa . Pada titik apapun, hanya 32 dari mereka yang secepatnya terlihat dengan perangkat lunak – 8 yaitu satu set register global (salah satunya, g0, sukar-kabel ke nol, sehingga hanya 7 dari mereka mampu dipakai sebagai register) dan 24 yang lain dari tumpukan dari register. 24 register ini membentuk apa yang disebut jendela mendaftar , dan memanggil fungsi / kembali, jendela ini digerakkan naik turun register stack. Setiap jendela mempunyai 8 register setempat dan saham 8 register dengan masing-masing jendela yang berdekatan. Register bersama digunakan untuk melewatkan parameter fungsi dan nilai kembali, dan register setempat digunakan untuk mempertahankan nilai-nilai setempat di seluruh pemanggilan fungsi.

The “Scalable” di SPARC berasal dari fakta bahwa spesifikasi SPARC memungkinkan implementasi untuk skala dari prosesor tertanam Facebook melalui prosesor server yang besar, semua inti berbagi sama (non-privilege) set arahan. Salah satu parameter arsitektur yang dapat skala adalah jumlah jendela register dijalankan; spesifikasi memungkinkan 3-32 jendela untuk dilakukan, sehingga pelaksanaannya mampu memilih untuk menerapkan semua 32 untuk menawarkan maksimum stack panggilan efisiensi, atau untuk menerapkan cuma 3 untuk menghemat waktu konteks switching, atau untuk menerapkan beberapa nomor antara mereka. arsitektur lain yang termasuk sejenis file mendaftar fitur termasuk Intel I960 , IA-64 , dan AMD 29000.

Arsitektur telah melalui beberapa revisi. Ini diperoleh hardware berkembang biak dan membagi fungsi dalam Versi 8. Yang substansial upgrade paling menghasilkan Versi 9, yang merupakan 64-bit dan data) SPARC spesifikasi menanggulangi (diterbitkan pada tahun 1994.

Dalam SPARC Versi 8, floating point file register mempunyai 16 presisi ganda register. Masing-masing mampu digunakan selaku dua presisi tunggal register, memberikan total 32 register presisi tunggal. Sebuah bilangan genap sepasang-asing dari register presisi ganda mampu dipakai sebagai quad presisi register, sehingga memungkinkan 8 quad presisi register. SPARC Versi 9 ditambah 16 lebih register presisi ganda (yang juga dapat diakses selaku 8 register quad presisi), tetapi register komplemen tidak mampu diakses sebagai register presisi tunggal.

Tagged menambah dan mengurangi arahan melaksanakan menambah dan menghemat nilai-nilai asumsi bahwa kedua bawah bit tidak berpartisipasi dalam perkiraan. Hal ini dapat berguna dalam pelaksanaan run time untuk ML , Lisp , dan bahasa yang serupa yang mungkin menggunakan format integer tag.